Speaker

Description

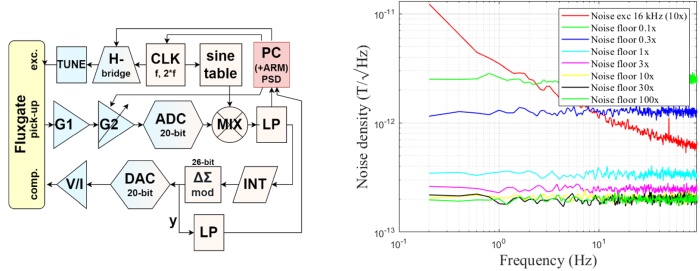

Construction of a digital lock-in amplifier [1] specifically designed for fluxgate sensor testing is presented together with first results. The instrument is based on a low-noise, multi-stage, fully-differential, analog front-end (G = 0.1 - 100$\times$), followed by 1 MSa/s, 20-bit, SAR-ADC (LTC2378) for high dynamic range. All necessary digital signal processing is done within a Cyclone V FPGA. Excitation signal for the fluxgate sensor is derived internally as well as the reference signal for sine table read-out (using 25-100 sine-wave samples per period of the fluxgate output signal at 2$f_{exc}$). The instrument currently supports several fixed excitation frequencies in the range of $f_{exc}$ = 5 to 20 kHz and H-bridge amplitudes (5-15 V) for excitation current tuning. Digital multiplier output signal is filtered using FIR filter (900 taps, >100 dB attenuation at 5 kHz) and decimated to 10 kSa/s for further processing (averaged PSD calculation) in the computer. In order to allow complete closed loop testing of the fluxgate sensors the device is equipped with a 20-bit R2-R DAC (DAC11001A) driven voltage-to-current converter. The resolution of the DAC is enhanced to 26-bits by $\Delta\sum$ modulation technique (digital resolution increase from 125 pT to 2 pT for $\pm$65 $\mu$T Full Scale range). In closed feedback mode, the instrument essentially forms a single-axis digital magnetometer [2], but with an ability to adapt to many different sensor types due to variable excitation and amplification settings. First measurements indicate comparable noise results to measurements done with SR830 (3.5 $\mathrm{pT/\sqrt{Hz}}$ at 1 Hz for a race-track fluxgate sensor, 16 kHz $f_{exc}$). Fig.1 shows the noise-floor for different input amplifier settings (for fluxgate sensor excitation disconnected). At 1 Hz the noise floor was below the measured sensor noise even for the lowest amplification setting (0.1$\times$).

Fig. 1 Block diagram of the lock-in based test setup (left), measured race-track fluxgate sensor noise and noise-floor for several input amplifier gain options (right).

Acknowledgements

This work was supported by a SGS grant at CTU in Prague (No. SGS22/170/OHK3/3T/13).

References

[1] G. Gervasoni, M. Carminati, and G. Ferrari, “FPGA-based lock-in amplifier with sub-ppm resolution working up to 6 MHz,” 2016 IEEE International Conference on Electronics, Circuits and Systems (ICECS). IEEE, Dec. 2016. doi: 10.1109/icecs.2016.7841146.

[2] H. O’Brien, P. Brown, T. Beek, C. Carr, E. Cupido, and T. Oddy, “A radiation tolerant digital fluxgate magnetometer,” Measurement Science and Technology, vol. 18, no. 11. IOP Publishing, pp. 3645–3650, Oct. 16, 2007. doi: 10.1088/0957-0233/18/11/050.